0

AD5371提供V(SS)从-16.5 V 到-4.5 V、V(DD)从9 V 到16.5 V宽电压范围内的可靠工作。负载电流为1mA时,输出放大器的裕量需求为1.4 V。

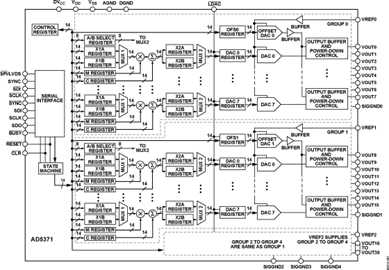

AD5371具有与SPI、QSPI 、MICROWIRE 和DSP接口标准兼容的高速串行接口,能够处理高达50 MHz的时钟速率。它还具有100 MHz的低压差分信号(LVDS)串行接口。

DAC寄存器在接收新数据时更新。通过将LDAC输入引脚拉低,所有的输出能够同时更新。每个通道都具有可编程增益和失调调整寄存器,允许去除增益和失调误差。

每个DAC输出能相对外部SIGGND输入被放大和缓冲。DAC输出也能够通过CLR引脚切换到SIGGND。

应用

*Protected by U.S. Patent No. 5,969,657; other patents pending.

Data Sheet, Rev. B, 3/08