AD9250是一款双通道14位ADC,最高采样速率250 MSPS,旨在为低成本、小尺寸、宽带宽、多功能通信应用提供解决方案。

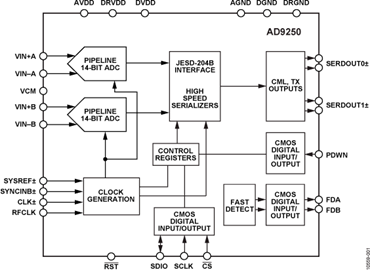

这款ADC内核采用多级、差分流水线架构,并集成了输出纠错逻辑。ADC内核具有宽带宽输入,支持用户可选的各种输入范围。集成基准电压源可简化设计。占空比稳定器可用来补偿ADC时钟占空比的波动,使转换器保持出色的性能。JESD204B高速串行接口可降低电路板布线要求,并减少接收器件所需的引脚数量。

默认情况下,ADC输出数据直接路由至两个JESD204B串行输出通道,这些输出设置为CML电平。四种模式支持M = 1或2(单通道或双通道转换器)与L = 1或2(单通道或双通道)的任意组合。在双通道ADC模式下,数据可以通过两个通道以最高采样速率250 MSPS发送。但是,如果通过一个通道发送数据,则仅支持最高125 MSPS的采样速率。器件提供同步输入(SYNCINB±和SYSREF±)。

需要时,灵活的关断选项可以明显降低功耗。每个通道通过专用快速检测引脚支持可编程超量程电平检测。

设置与控制编程利用三线式SPI兼容型串行接口来完成。

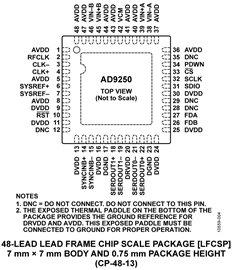

AD9250采用48引脚LFCSP封装,额定温度范围为-40°C至+85°C工业温度范围。

中国,北京 JESD204BSerDes(串行器/解串器)技术,最近该系列推出新品AD9250-FMC-250EBZ套件。数字和模拟设计人员可以利用AD9250-FMC-250EBZ套件简化并快速完成高速http://www.analog.com/zh/pr0228/eval-ad9250· 了解有关JESD204B

FPGA开发平台兼容的 FPGA 夹层卡 (FMC) 系列采用 JEDEC JESD204B SerDes(串行器/解串器)技术,最近该系列推出新品 AD9250-FMC-250EBZ 套件。数字和模拟设计人员可以利用 AD9250-FMC-250EBZ 套件简化并快速完成高速JESD204B ADC-FPGA平台的原型开发。 AD9250-FMC-

为解决这一需求,模数转换器AD9250。AD9250 ADC是市场上首款完全达到JESD204B Subclass 1确定性延迟要求的250 MSPS ADC,此功能通过

Analog Devices, Inc.和Xilinx, Inc.日前宣布,Kintex-7 FPGA中的Xilinx JESD204 LogiCORE IP和ADI AD9250模数高速数据转换器之间的

中国北京2013年9月24日ADI AD9250模数高速数据转换器之间的JESD204B实现互操作。实现逻辑和数据转换器器件之间的JESD204B互操作性,是促进该新技术广泛运用的一个重大里程碑。