0

AD9262具有阻性输入阻抗,可显著降低对驱动器放大器的要求。此外,32倍过采样五阶连续时间环路滤波器可显著衰减带外信号和混叠,因而输入端无需外部滤波器。

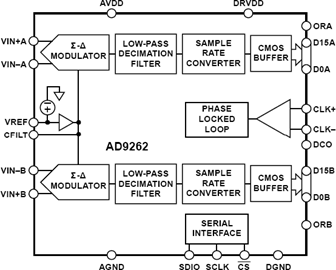

外部时钟输入或集成的整数N分频锁相环(PLL)提供过采样连续时间西格马-得尔塔调制器所需的640 MHz内部时钟。片内抽取滤波器和采样速率转换器可将调制器数据速率从640 MSPS降至用户定义的输出数据速率(30 MSPS至160 MSPS),从而实现更高效、更直接的接口。

AD9262集成一个直流校正和正交估算模块,用于校正两个通道之间的增益和相位失配。在直接变频接收机等复信号处理应用中,此功能模块可发挥重要作用。

数字输出数据格式为偏移二进制、格雷码或二进制补码。数据时钟输出(DCO)用来确保接收逻辑以正确的时序工作。AD9262还新增一项特性,可以在一条16位总线上交错提供通道A与通道B数据,从而简化电路板布线。

该ADC提供2.5 MHz、5 MHz和10 MHz三种不同带宽选择,采用1.8 V模拟电源和1.8 V至3.3 V数字电源工作,功耗为675 mW。AD9262采用64引脚LFCSP封装,额定温度范围为-40°C至+85°C工业温度范围。

产品聚焦

应用

16-bit ad9261与ad9262 ctsd转换器,以及ad9267 ctsd解调器将业界最小噪声和高动态范围与10mhz带宽结合在一起。