0

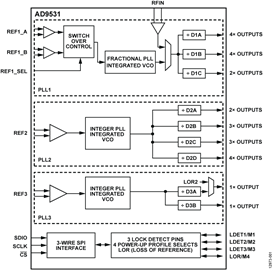

AD9531提供一个多路输出时钟发生器和三个具有可编程输出频率和格式的片上锁相环内核(PLL)内核。

PLL1提供两个参考输入和10个输出,包括四种用户可选环路配置。 PLL具有全集成式环路滤波器,只需单个外部电容(或者串联RC网络)。 PLL1提供高达400 MHz的宽输出频率范围,能够使用外部压控振荡器(VCXO)和环路滤波器,而不是集成式压控振荡器(VCO)和环路滤波器工作。

PLL2是整数N分频PLL,提供单个参考输入和12个输出。 PLL2通过REF2_x源同步高达400 MHz的输出频率,并将输出时钟与输入参考同步。

PLL3提供单个参考输入和两个输出。 PLL3通过REF3_x源同步高达400 MHz的输出频率,并将输出时钟与输入参考同步。

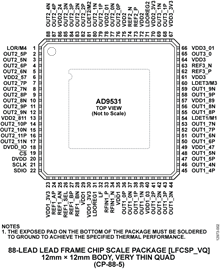

AD9531采用88引脚LFCSP封装,额定工作温度范围为-40°C至+85°C。

在整篇数据手册中,多功能引脚(如LOR/M4)由整个引脚名称或引脚的单个功能表示(例如LOR即表示仅与此功能相关)。 在其他情况下,本数据手册中的文本和数字表示通道,而不是引脚。 例如,REF_A指REF_A通道,而不是REF_AP和REF_AN引脚。 同样,OUT3_1指PLL3的通道1,而不是OUT3_1P和OUT3_1N引脚。 此外,引脚对缩写符号将取代明确指示各引脚(例如,REF_Ax表示REF_AN和REF_AP引脚。)。

应用