0

|

|

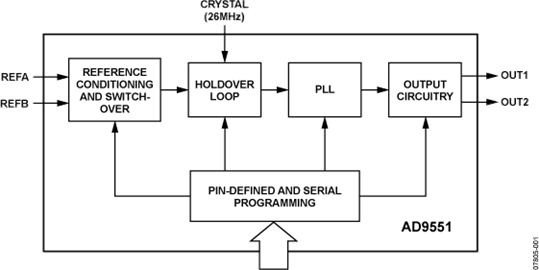

参考调节和转换电路在内部使两个参考同步,以便一个参考失效时,输出端实际上不出现相位扰动现象。

AD9551采用一个26 MHz外部晶体(标称值)和内部DCXO来提供保持模式工作。如果两个参考都失效了,该器件会维持一个稳定的输出信号。

小数N分频PLL可实现超精细的输出频率调谐精度。所有目前定义的网络标准(包括前向纠错率)都可能实现(假设采用一个26 MHz的晶体)。

AD9551具备引脚可选的预置分频器值,从而提供频比分类。由于具备对大多数所需频比进行编程的能力,因此SPI接口拥有更多灵活性。

应用

(ADI)最新推出一款时钟发生器AD9551,可在多标准网络和通信基础设施系统中简化时钟设计,并减少对振荡器需求。AD9551时钟发生器采用一个新型的、由ADI公司设计的简化架构,它可以生成并转换多倍精度的网络时钟频率,使之能够替换多达五个振荡器。除节省电路板空间之外,相对于分立的振荡器,AD9551能提供更