0

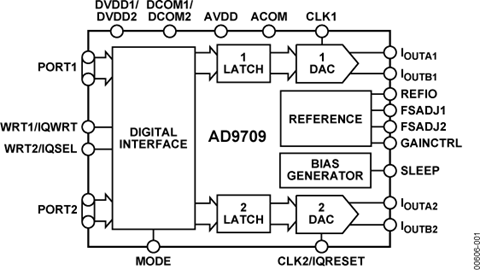

AD9709针对通信应用中的I数据与Q数据处理进行了优化。数字接口含有两个双缓冲锁存器以及控制逻辑。独立的写输入允许数据彼此独立地写入两个DAC端口。独立的时钟可控制各DAC的更新速率。

利用模式控制引脚,AD9709可以与两个单独的数据端口接口,或与单个交错式高速数据端口接口。在交错模式下,输入数据流被解复用为原始I数据与Q数据,然后锁存。随后,I数据与Q数据由两个DAC转换,并以一半输入数据速率更新。

GAINCTRL引脚允许以两种模式设置两个DAC的满量程电流(IOUTFS)。可以用两个外部电阻独立设置各DAC的IOUTFS,也可以用一个外部电阻设置两个DAC的IOUTFS。有关此特性的重要日期码信息,请参阅“增益控制模式”部分。

这些DAC采用分段电流源架构,并结合专有开关技术,可减小突波能量,并使动态精度达到最大。每个DAC均提供差分电流输出,从而支持单端或差分应用。两个DAC可以同时更新,并提供一个20 mA的标称满量程电流。各DAC之间的满量程电流匹配精度可达到0.1%以内。

AD9709采用先进的低成本CMOS工艺制造,采用3.3 V或5 V单电源供电,功耗为380 mW。

产品聚焦

应用

【用 途】 【性能 参数】【互换 兼容】

点击下载文档