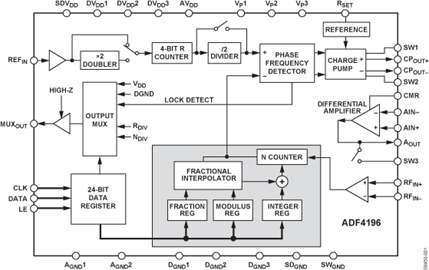

ADF4196由低噪声数字鉴频鉴相器(PFD)和精密差分电荷泵组成。还有一个差分放大器,用来将电荷泵的差分输出转换为外部电压控制振荡器(VCO)的单端电压。西格马-得尔塔型小数插值器与N分频器一起使用,能够实现可编程模数小数N分频。此外,4位参考(R)分频器和片内倍频器允许PFD输入端的参考信号(REFIN)频率为可选值。

如果频率合成器与外部环路滤波器和VCO一起使用,则可以实现完整的锁相环(PLL)。开关结构确保PLL能在GSM时隙保护期间内建立,而无需第二PLL及相关的隔离开关。与以前的乒乓式GSM PLL结构相比,这种结构能节省成本,降低复杂度,减小PCB面积,并减少屏蔽和特性测试工作。

应用

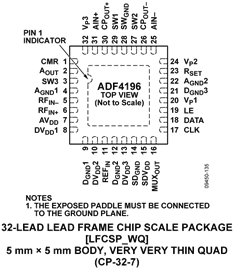

【用 途】 PLL频率合成器【性能 参数】 采用32脚LFCSP封装,超快建立时间的6GHz小数N分频PLL,专门设计用来满足通信基础设施和脉冲多普勒雷达应用的GSM/EDGE锁定时间要求。结合外部环路滤波器和VCO使用时,可以实现低于5us的锁定时间。它由低噪声数字鉴频鉴相器(PFD)和精密差分电荷泵组成。 &nb

(ADI),最近推出两款新的 PLL 频率合成器 ADF4151 和 ADF4196 ,这些器件能够提供最大的灵活性和最佳的相位噪声性能,可简化多种应用的设计,包括通信基础设施基站、脉冲和多普勒雷达应用

span>ADF4196锛岃繖浜涘櫒浠惰兘澶熸彁渚涙渶澶х殑鐏垫椿鎬у拰鏈€浣崇殑鐩镐綅鍣0鎬ц兘锛屽彲绠€鍖栧

ADI,最近推出两款新的PLL频率合成器ADF4151和ADF4196,这些器件能够提供最大的灵活性和最佳的相位噪声性能,可简化多种应用的设计,包括通信基础设施基站、脉冲和多普勒雷达应用、测试与测量仪器设备