0

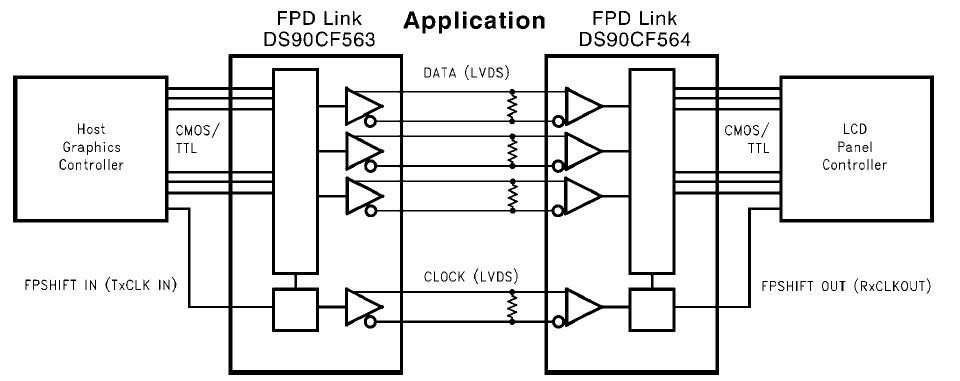

DS90CF563发射机将21位CMOS/TTL数据转换为3个LVDS(低压差分信令)数据流。锁相传输时钟与数据流在第四个LVDS链路上并行传输。在发送时钟的每个周期中,21位输入数据被采样和发送。DS90CF564接收器将LVDS数据流转换成21位CMOS/TTL数据。在65mhz的传输时钟频率下,18位RGB数据和3位LCD定时和控制数据(FPLINE, FPFRAME, DRDY)以455mbps的速率每LVDS数据通道传输。使用65mhz时钟,数据吞吐量为每秒171兆字节。这些设备提供了下降边缘数据频闪,方便与各种图形和LCD面板控制器的界面。

该芯片组是解决电磁干扰和电缆尺寸问题的理想手段,与宽,高速TTL接口。