0

HMC7043旨在满足多载波GSM和LTE基站设计的要求,并通过多种时钟管理和分配特性来简化基带和无线电卡时钟树的设计

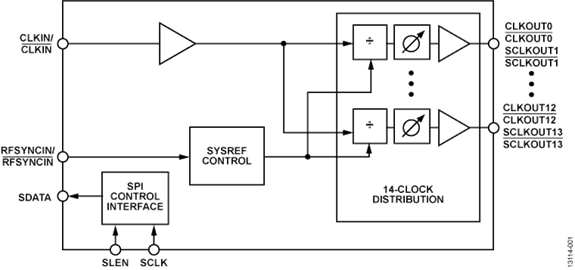

HMC7043提供14路低噪声且可配置的输出,可以灵活地与基站收发台(BTS)系统中的许多不同器件接口,如数据转换器、本振、发射/接收模块、现场可编程门阵列(FPGA)和数字前端ASIC等。 HMC7043可生成符合JESD204B接口要求的多达7个DCLK和SYSREF时钟对。

系统设计人员可以生成更少的DCLK和SYSREF对,并针对独立的相位和频率配置其余的输出信号路径。 DCLK和SYSREF时钟输出均可配置为支持CML、LVDS、LVPECL和LVCMOS等不同的信号标准,不同的偏置条件则可调整变化的板插入损耗。

HMC7043独特的特性之一是对14个通道分别进行独立灵活的相位管理。 所有14个通道均支持频率和相位调整。 这些输出还可针对50 欧姆或100 欧姆内部和外部端接选项进行编程。

HMC7043器件具有RF SYNC功能,支持确定性同步多个HMC7043器件,即确保所有时钟输出从同一时钟沿开始。 可通过改写嵌套式HMC7043或SYSREF控制单元/分频器,然后重新启动具有新相位的输出分频器来实现。

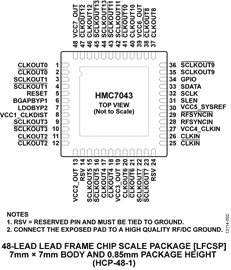

HMC7043采用48引脚、7 mm × 7 mm LFCSP封装,且裸露焊盘接地。

应用