摘要: 在FPGA中,随着信号处理的层次加深,对信号进行乘、累加、滤波等运算后,可能输入时仅为8位位宽的信号会扩展成几十位位宽,位宽越宽,占用的硬件资源就越多,但位宽超过一定范围后,位宽的增宽并不会对处理精度带来显著的改善,这时就需要对信号进行截位。写过FPGA HDL代码的童鞋都应该知道,截位是最为经常的一种操作。

在FPGA中,随着信号处理的层次加深,对信号进行乘、累加、滤波等运算后,可能输入时仅为8位位宽的信号会扩展成几十位位宽,位宽越宽,占用的硬件资源就越多,但位宽超过一定范围后,位宽的增宽并不会对处理精度带来显著的改善,这时就需要对信号进行截位。写过FPGA HDL代码的童鞋都应该知道,截位是最为经常的一种操作。

一般来说,截位只需截掉低几位即可,这是最简单的做法;对于无符号数来说,这样做也没有问题;当然也有四舍五入的截位方法,就是给次低位加一后再进行截位。

下面讨论三种截位截略:1)直接截位;2)负数截位后加1;3)负数取绝对值后再截位。在matlab中模拟FPGA截位过程,运行如下一段程序,得到四幅图。

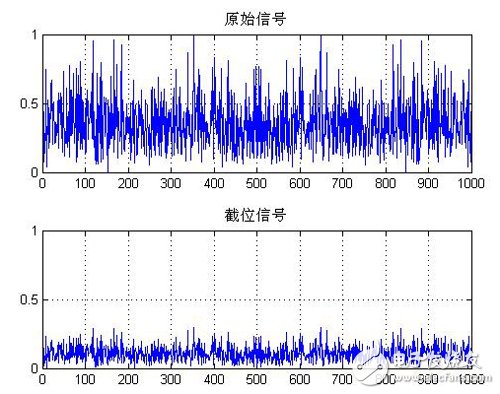

图一:直接截去低五位

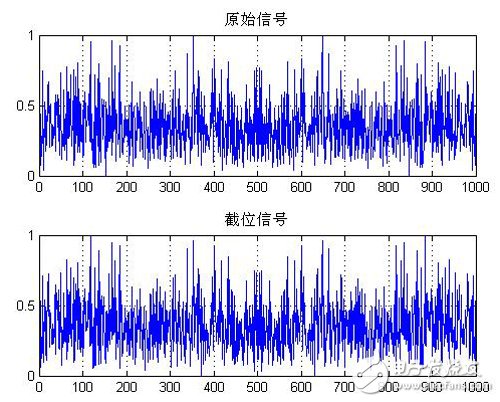

图二:直接截去低12位

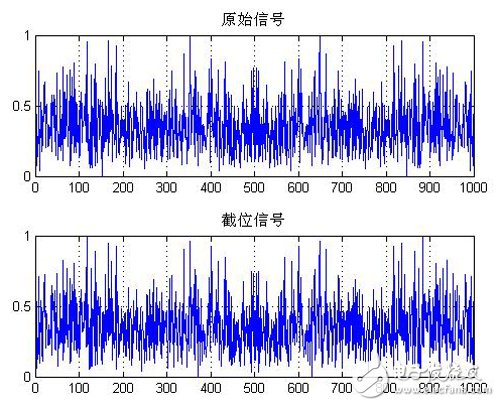

图三:截去低12位且负数截位后加一

图四:截去低12位且负数取绝对值后再截位,截完位再变回原先的符号

由图三和图四可以看出,采用第二种和第三种截位策略后,直流分量消失。

其实第三种截位策略是达到了这样一种效果:一对相反数在截位后仍然是一对相反数。这种效果在直接截位时对于奇数来说是达不到的。

其实直接截位之所以出现直流分量可以这样直观的来认识:从matlab程序中也可以看出,对于FPGA信号截位来说,实际上就是向下取整。

对于有符号数来讲,正数向下取整在数轴上是向原点零靠近,然后负数向下取整则是远离原点零了,这是因为负数以补码形式表示,它的补码所对应的无符号数经截位后向原点零靠近了,换算成有符号的负数时,则是远离原点零了。

因此截位实际造成的效果是信号整体向负无穷方向平移了,即对于一个白噪声序列来讲,原本均值为零,截位后均值变为了负数。

了解更多相关设计技术信息,请点击华强旗舰电子圈(http://www.hqbuy.com/dzq/dzqsy.html)!

社群二维码

关注“华强商城“微信公众号

Copyright 2010-2023 hqbuy.com,Inc.All right reserved. 服务热线:400-830-6691 粤ICP备05106676号 经营许可证:粤B2-20210308