摘要: 本文将详细给大家介绍计数器芯片74LS162的中文资料,其中包括74ls162的引脚图及功能、真值表、极限值、逻辑图、推荐工作条件、静态动态特性和设计进制电路等方面知识。

本文将详细给大家介绍计数器芯片74LS162的中文资料,其中包括74ls162的引脚图及功能、真值表、极限值、逻辑图、推荐工作条件、电气特性和应用电路等方面知识。

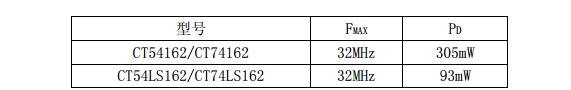

芯片74ls162是十二管脚的为可预置的十进制同步计数器,其主要电特性的典型值如下:

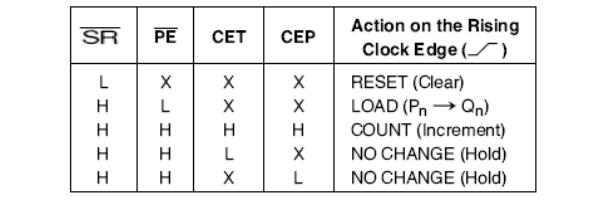

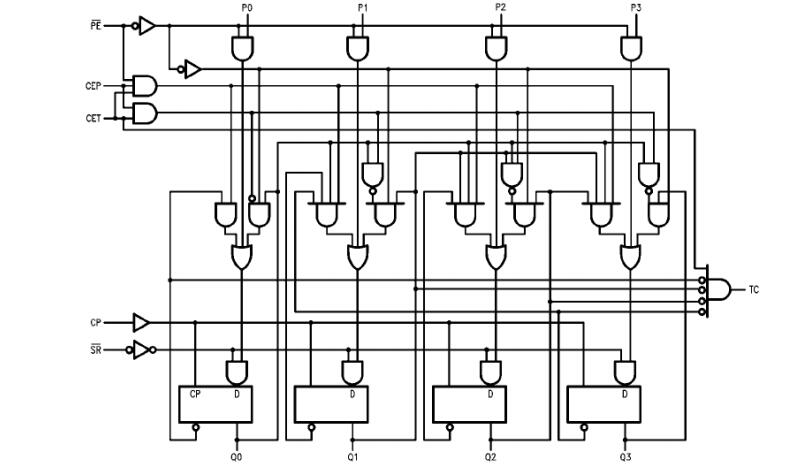

74ls162的清除端是同步的。当清除端/SR为低电平时,在时钟端CP上升沿作用下,才可完成清除功能。

74ls162的预置是同步的。当置入控制器/PE为低电平时,在CP上升沿作用下,输出端Q0-Q3与数据输入端P0-P3一致。对于54/74162,当CP由低至高跳变或跳变前,如果计数控制端CEP、CET为高电平,则/PE应避免由低至高电平的跳变,而54/74LS162无此种限制。

74ls162的计数是同步的,靠CP同时加在四个触发器上而实现的。当CEP、CET均为高电平时,在CP上升沿作用下Q0-Q3同时变化,从而消除了异步计数器中出现的计数尖峰。对于54/74162,只有当CP为高电平时,CEP、CET才允许由高至低电平的跳变,而54/74LS162的CEP、CET跳变与CP无关。

162有超前进位功能。当计数溢出时,进位输出端(TC)输出一个高电平脉冲,其宽度为Q0的高电平部分。在不外加门电路的情况下,可级联成N位同步计数器。对于54/74LS162,在CP出现前,即使CEP、CET、/SR发生变化,电路的功能也不受影响。

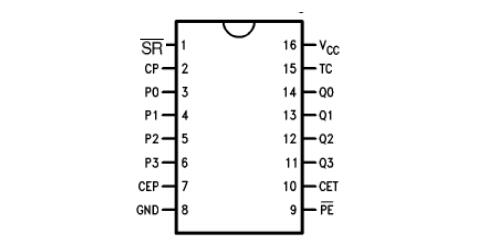

74ls162管脚功能说明:

TC 进位输出端

CEP 计数控制端

Q0-Q3 输出端

CET 计数控制端

CP 时钟输入端(上升沿有效)

/SR 异步清除输入端(低电平有效)

/PE 同步并行置入控制端(低电平有效)

74ls162功能说明:

H-高电平

L-低电平

X-任意

电源电压------------------------------------------------7V

输入电压

54/74162-----------------------------------------5.5V

54/74LS162---------------------------------------7V

CEP与CET间电压

54/74162-----------------------------------------5.5V

工作环境温度

54&TImes;&TImes;&TImes;-------------------------------55~125℃

74&TImes;××------------------------------------0~70℃

贮存温度---------------------------------------65~150℃

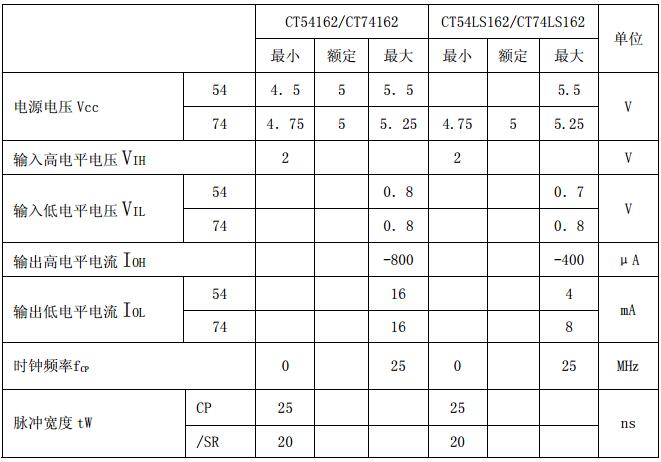

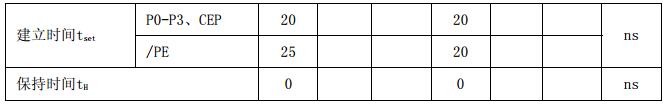

【1】:测试条件中的“最大”和“最小”用推荐工作条件中的相应值。

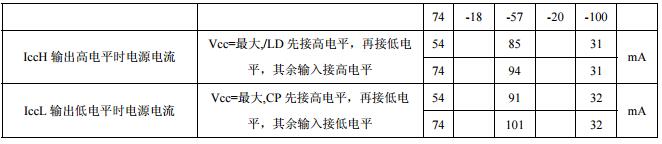

【2】:fmax-最大时钟频率

tPLH-输出由低到高电平传输延迟时间

tPHL-输出由高到低电平传输延迟时间

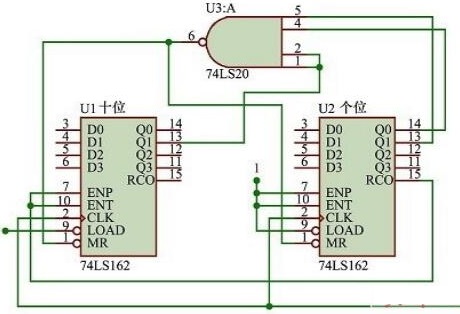

采用同步置零74LS162计数器来设计24进制计数器,反馈代码必须是(23)10相应的8421BCD码为00100011.由此可见反馈信号应取自十位芯片的Q1及个位芯片的Q1和Q0,相应的与非门应改成四输入端与非门。用74LS162并行置零法设计24进制计数器的电路图如图所示。

社群二维码

关注“华强商城“微信公众号

Copyright 2010-2023 hqbuy.com,Inc.All right reserved. 服务热线:400-830-6691 粤ICP备05106676号 经营许可证:粤B2-20210308