摘要: 74LS73是双列直插式JK触发器IC。它包含两个具有独立JK,时钟和直接清除输入的独立JK触发器。74LS73是一个正脉冲触发触发器。

74LS73是双列直插式JK触发器IC。它包含两个具有独立JK,时钟和直接清除输入的独立JK触发器。74LS73是一个正脉冲触发触发器。

| Pin Number | Pin Name | Description |

| 4 | Vcc | Powers the IC typically with 5V |

| 13 | Ground | Connected to the ground of the system |

JK Flip Flop – 1 / JK Flip Flop - 2

| 1,5 | Clock-1/ Clock-2 | These pins must be provided with clock pulse for the flip flop |

| 2,6 | Clear-1 / Clear-2 | Resets the flip flop by clearing its memory |

| 3,12 | K-1/ K-2 | Input pin of the Flip Flop |

| 16,7 | J-1 / J-2 | Another Input pin of the Flip Flop |

| 15, 10 | Q-1(bar) / Q-2 (bar) | Inverted output pin of Flip Flop |

| 14,11 | Q-1 / Q-2 | Output Pin of the Flip Flop |

双路JK触发器封装IC

工作电压:5V

高电平输入电压:2 V

低电平输入电压:0.8 V

工作温度范围= -55至125°C

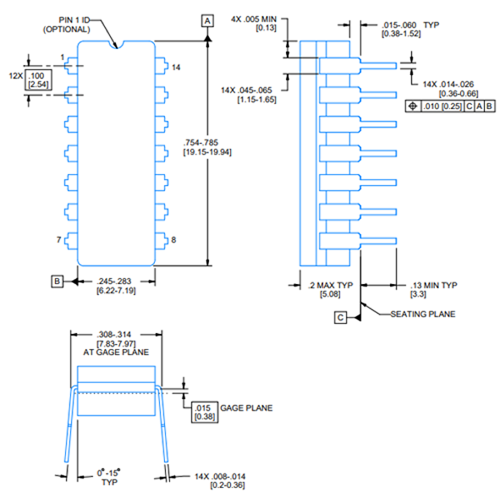

提供14引脚PDIP,GDIP,PDSO封装

等效于74LS73: MC74HC73A

替代品JK触发器: 74LS76、74LS107、4027B

74LS73是双列直插式JK触发器 IC。这意味着它内部有两个JK触发器,每个触发器都可以根据我们的应用单独使用。当时钟为高电平时,JK输入被加载到主机中,并在从高到低的跳变中传输到从机。该IC可用于闩锁应用,或用作项目的小型可编程存储器。

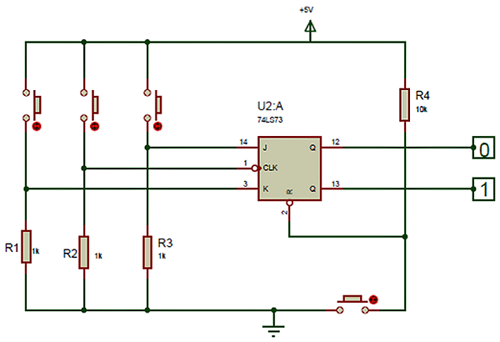

如前所述,74LS73具有两个负沿触发的JK触发器,该IC由+ 5V供电。下面的电路显示了JK触发器工作的典型示例连接

J和K引脚是触发器的输入引脚,Q和Q条形引脚是输出引脚。输入引脚通过一个1k电阻下拉至地,这样我们可以避免引脚处于悬空状态。也就是说,当不按下按钮时,该引脚将保持接地;当按下按钮时,该引脚将被保持供电。

复位按钮应通过一个1K 电阻上拉,当接地时将复位触发器。JK触发器的时钟信号负责更改输出状态。触发器将仅在时钟信号的上升沿期间改变其输出。这里的时钟信号只是一个按钮,但可以像PWM信号一样是脉冲类型。可以从下面的真值表确定触发器的输出状态。

通常,在IC正常运行期间,复位引脚将被设置为高电平,并且已知频率的时钟脉冲将被提供给时钟引脚,然后J和K的值将根据输入信号而变化,并且相应的输出将为在Q和Q条形针上获得。

移位寄存器

存储器/控制寄存器

EEPROM电路

闩锁装置

社群二维码

关注“华强商城“微信公众号

Copyright 2010-2023 hqbuy.com,Inc.All right reserved. 服务热线:400-830-6691 粤ICP备05106676号 经营许可证:粤B2-20210308