摘要: 德州仪器(TI)TMS320VC5503定点数字信号处理器(DSP)基于TMS320C55x DSP生成CPU处理器内核。德州仪器(TI)的TMS320C55x DSP架构通过提高并行度并集中精力降低功耗来实现高性能和低功耗。

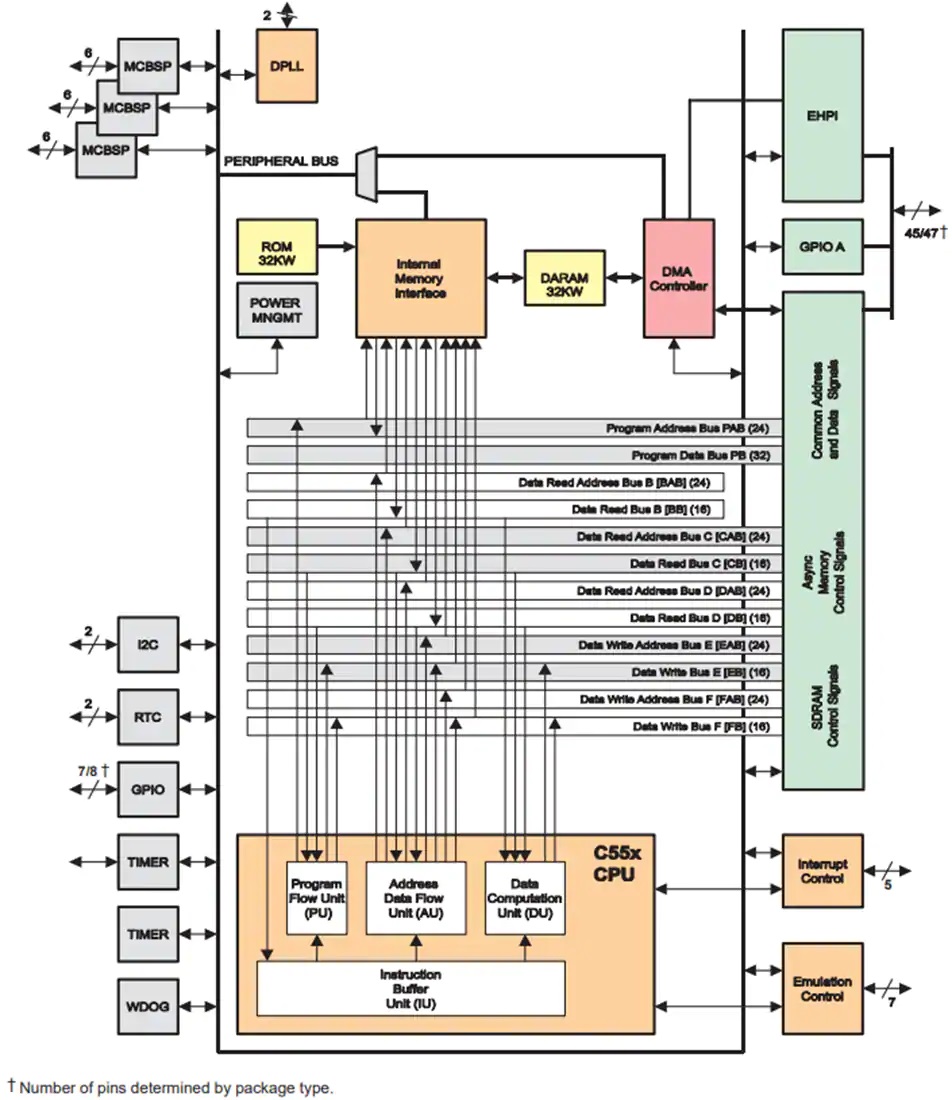

德州仪器(TI)TMS320VC5503定点数字信号处理器(DSP)基于TMS320C55x DSP生成CPU处理器内核。德州仪器(TI)的TMS320C55x DSP架构通过提高并行度并集中精力降低功耗来实现高性能和低功耗。CPU支持内部总线结构,该结构由一个程序总线,三个数据读取总线,两个数据写入总线以及专用于外围设备和DMA活动的附加总线组成。这些总线提供了在一个周期内最多执行三个数据读取和两个数据写入的功能。并行而言,DMA控制器每个周期最多可以执行两次数据传输,而与CPU活动无关。

TMS320C55x CPU提供了两个乘法累加(MAC)单元,每个单元可以在一个周期内进行17位x 17位乘法。附加的16位ALU支持中央40位算术/逻辑单元(ALU)。ALU的使用在指令集的控制下,具有优化并行活动和功耗的能力。这些资源在TMS320C55x CPU的地址单元(AU)和数据单元(DU)中进行管理。TMS320C55x DSP生成支持可变字节宽度的指令集,以提高代码密度。指令单元(IU)从内部或外部存储器执行32位程序提取,并将针对程序单元(PU)的指令排队。程序单元对指令进行解码,将任务定向到AU和DU资源,并管理完全受保护的管道。

TMS320VC5503上的64K字节片上存储器足以用于许多小型手持式设备,便携式个人设备,游戏设备和个人医疗设备。这些设备中的许多设备通常需要64K字节或更少量的片上内存,并且需要在待机模式下运行60%至70%以上的时间。对于需要超过64K字节片上存储器但少于128K字节存储器的应用,德州仪器(TI)提供了基于TMS320C55x DSP内核的TMS320VC5507。通用输入和输出功能为LCD,键盘和媒体接口的状态,中断和位I / O提供足够的引脚。并行接口以两种模式工作,或者作为使用HPI端口的微控制器的从设备,或者作为使用异步EMIF的并行媒体接口。

TMS320C5503外围设备套件包括一个外部存储器接口(EMIF),可以无缝访问EPROM和SRAM等异步存储器,以及同步DRAM等高速高密度存储器。其他外设包括实时时钟,看门狗定时器和I 2C多主从接口。三个全双工多通道缓冲串行端口(McBSP)提供了到各种行业标准串行设备的无缝接口以及多达128个独立启用的通道的多通道通信。增强型主机端口接口(HPI)是16位并行接口,用于提供主机处理器对TMS320C5503上32K字节内部存储器的访问。可以以多路复用或非多路复用模式配置HPI,以为多种主机处理器提供无缝接口。DMA控制器无需CPU干预即可提供六个独立通道上下文的数据移动,每个周期最多提供两个16位字的DMA吞吐量。两个通用定时器,最多八个专用通用I / O(GPIO)引脚,

高性能,低功耗,定点TMS320C55数字信号处理器

9.26、6.95、5ns指令周期时间

108、144、200MHz时钟频率

每个周期执行一条/两条指令

双乘法器[每秒高达4亿次乘法累加(MMACS)]

两个算术/逻辑单元(ALU)

三个内部数据/操作数读取总线和两个内部数据/操作数写入总线

32K×16位片上RAM,由

64KB双访问RAM(DARAM)8个4K×16位块

64 KB的一个等待状态的片上ROM(32K×16位)

8M×16位最大可寻址外部存储空间(同步DRAM)

16位外部并行总线存储器支持以下任一

具有GPIO功能的外部存储器接口(EMIF)和与接口的无缝接口

异步静态RAM(SRAM)

异步EPROM

同步DRAM(SDRAM)

具有GPIO功能的16位并行增强型主机端口接口(EHPI)

六个设备功能域的可编程低功耗控制

基于片上扫描的仿真逻辑

片上外设

两个20位定时器

看门狗定时器

六通道直接存储器访问(DMA)控制器

三个多通道缓冲串行端口(McBSP)

可编程锁相环时钟发生器

七个(LQFP)或八个(BGA)通用I / O(GPIO)引脚和一个通用输出引脚(XF)

集成电路间(I 2 C)多主从接口

带有晶体输入的实时时钟(RTC),独立的时钟域,独立的电源

IEEE Std 1149.1(JTAG)边界扫描逻辑

配套

144端子薄型四方扁平包装(LQFP)(后缀PGE)

179端子MicroStar BGA(球栅阵列)(GHH和ZHH后缀)

1.2V内核(108MHz),2.7V至3.6VI / O

1.35V内核(144MHz),2.7V至3.6VI / O

1.6V内核(200MHz),2.7V至3.6VI / O

社群二维码

关注“华强商城“微信公众号

Copyright 2010-2023 hqbuy.com,Inc.All right reserved. 服务热线:400-830-6691 粤ICP备05106676号 经营许可证:粤B2-20210308