摘要: Astera Labs PT4161L PCI Express Gen-4 x16低延迟智能重定时器集成无缝根联合体和结束点(一个或多个)之间的16GT由>28分贝延伸到达/秒

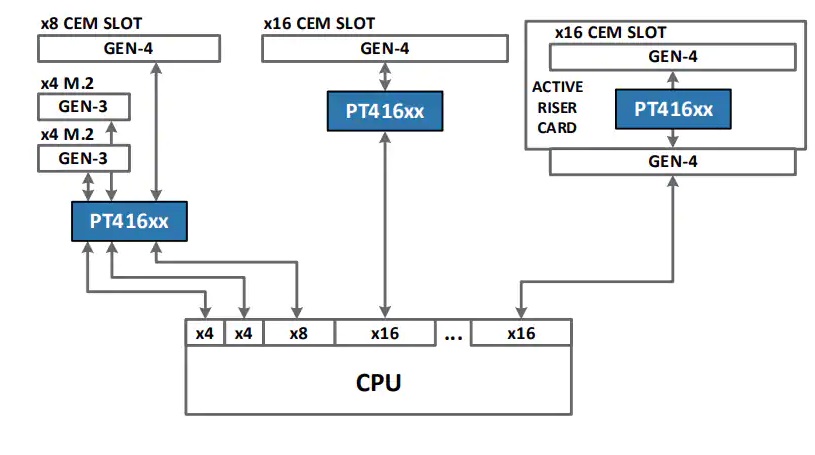

Astera Labs PT4161L PCI Express Gen-4 x16低延迟智能重定时器集成无缝根联合体和结束点(一个或多个)之间的16GT由>28分贝延伸到达/秒。PT4161L符合所有PCIe 4.0速率和重定时器功能要求,同时支持更多系统拓扑,并降低了总解决方案成本。PT4161L消除了以数据为中心的应用中PCI-Express(PCIe)4.0互连的信号完整性问题,非常适合空间受限的应用,例如系统板和转接卡。

Astera Labs PT4161L PCI Express重定时器具有创新的协议无中断低延迟架构,可显着减少延迟,同时对系统软件透明。该体系结构与根联合体和端点一起参与链路均衡,以优化链路性能。PT4161L可以独立地调整其延迟,以在正常操作的链路状态(L0)期间最大化性能,同时保持协议的互操作性。

PT4161L细分为一个x16链接,两个x8链接,四个x4链接,八个x2链接等,从而支持各种端点和端口配置。可通过每个链路诊断信息(例如,链路状态历史记录和电气裕度)访问带内(接收方裕度)和带外(SMBus)方法。每个链接独立运行。

PT4161L具有一个标准的PCIe 100MHz HCSL输入时钟,并提供一个100MHz HCSL输出时钟来驱动系统中的其他重定时器设备或PCIe组件。

PT4161L智能重定时器提供紧凑的设计,最少的支持电路和集成的AC耦合电容器。引脚排列基于英特尔Retimer补充规范,并使用8.9mm x 22.8mm的倒装芯片CSP封装。

与PCIe Gen-4 / 3/2/1兼容

具有自动链路均衡的16GT / s,8GT / s,5GT / s和2.5GT / s数据速率

低延迟模式启用高速缓存一致性链接

16条带灵活链路分叉的车道,包括1x16、2x8、4x4、8x2等

以16gt / s的速度将范围扩展到> 28db,从而实现了低成本的PCB材料和连接器

接收器和发送器性能超过PCI Express基本规范要求

无需系统软件

BGA封装尺寸经过优化,可用于电路板布线

集成交流耦合电容器可减小解决方案尺寸并提高信号完整性

支持热插拔

支持接收器在时序和电压上的通道裕度

支持SRIS,SRNS和通用时钟系统

支持从机环回

支持带车道反转的系统并实现自动极性校正

低功耗高级CMOS工艺

HCSL参考时钟输出消除了时钟缓冲器以驱动下游PCIe组件

用于车队管理,大规模服务器部署的高级带内和带外诊断

功能齐全的C和Python SDK,可快速集成高级诊断功能

通过SMBus或EEPROM进行设备配置

IEEE 1149.6 AC-JTAG边界扫描

引脚和寄存器兼容的重定时器的完整产品组合使性能轻松扩展至PCI Express Gen-5

服务器和高性能PC主板

PCIe Riser卡和附加卡

服务器到服务器的电缆接口

NVMe JBOF,GPU /深度学习加速器

社群二维码

关注“华强商城“微信公众号

Copyright 2010-2023 hqbuy.com,Inc.All right reserved. 服务热线:400-830-6691 粤ICP备05106676号 经营许可证:粤B2-20210308