摘要: 利用FPGA进行数字信号处理时,信号中的直流分量通常需要去除,而直流分量在AD前段就存在,如果采用模拟电路去除直流分量比较复杂,因此通常在AD后端数字域去除直流分量。

利用FPGA进行数字信号处理时,信号中的直流分量通常需要去除,而直流分量在AD前段就存在,如果采用模拟电路去除直流分量比较复杂,因此通常在AD后端数字域去除直流分量。

在FPGA中,常规去直流的方法是先对信号进行累加,然后对累加值进行移位即可得到直流分量,如累加8192个数据,则直流分量可由累加值右移13位得到。

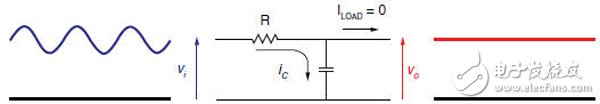

本文介绍一种根据Xilinx FPGA中DSP48E1资源设计的去直流模块,其基本原理采用一阶滤波器,如图1所示,通过一个一阶RC电路,在V0端可等效一个低通滤波器,得到直流分量。

图1

由上式可推导出,定义系数,由此可得到下式:

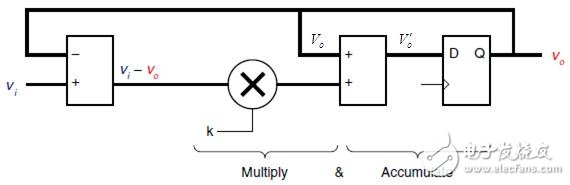

由上式可得到如图2所示结构:

图2

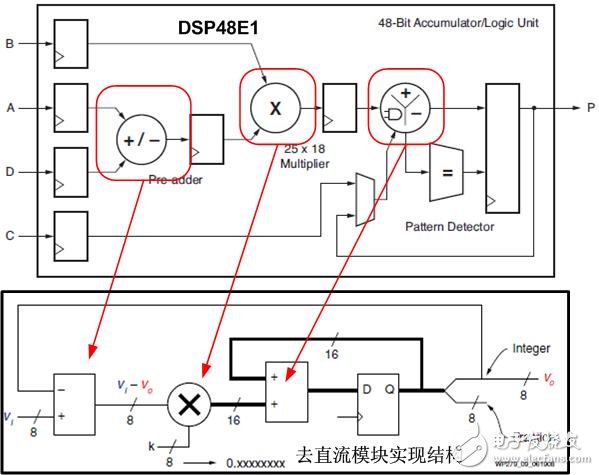

仔细观察发现图2中结构与Xilinx FPGA的DSP48E1结构十分相似,如图3所示,两个结构做了类比,其中Vi - Vo的减法可由DSP48E1中的Pre-Adder实现,k*(vi - vo)的乘法可由DSP48E1中的MulTIpler实现,而Vo + k*(vi - vo)加法可由DSP48E1中的Accumulator实现。

因此实现这个去直流模块只需1个DSP48E1资源,并且在Xilinx 7系列FPGA中,DSP48E1最大支持25-bit的Pre-adder、25*18-bit的MulTIpler和48-bit的Accumulator,基本可满足常规处理。

图3

了解更多相关设计技术信息,请点击华强旗舰电子圈(http://www.hqbuy.com/dzq/dzqsy.html)!

社群二维码

关注“华强商城“微信公众号

Copyright 2010-2023 hqbuy.com,Inc.All right reserved. 服务热线:400-830-6691 粤ICP备05106676号 经营许可证:粤B2-20210308