摘要: 74LS93由两个向上计数器的4位二进制计数器。该IC由一个模式2向上计数器和一个模式8向上计数器组成。可以组合为mod-8计数器或除以2或除以8的应用程序。它使用四个JK触发器构建。

74LS93由两个向上计数器的4位二进制计数器。该IC由一个模式2向上计数器和一个模式8向上计数器组成。可以组合为mod-8计数器或除以2或除以8的应用程序。它使用四个JK触发器构建。

.png)

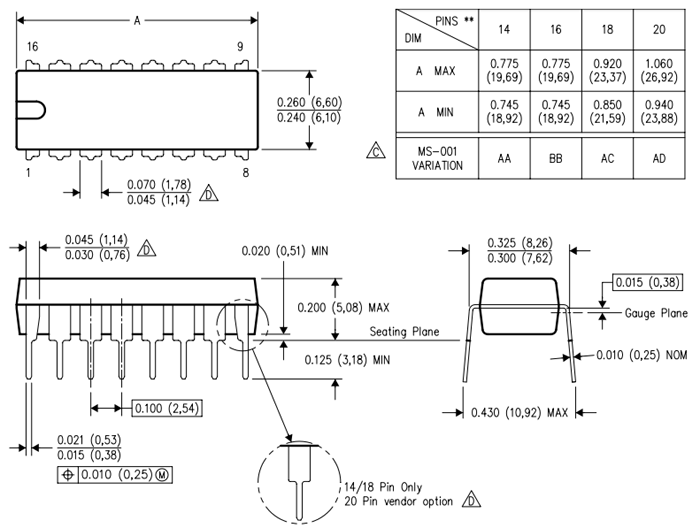

| Pin Number | Pin Name | Description |

| 1,2,3,6 | NC | No Connection |

| 4,5,8,9 | Q0, Q1, Q2, Q3 | Output pins |

| 7 | Ground | Connected to ground of the system |

| 10 | CP0 | Clock Input – divide by 2 |

| 11 | CP1 | Clock Input – divide by 8 |

| 12,13 | MR | Master Reset – Clear Input |

| 14 | Vcc | Supply voltage – 4.5V to 5.5V |

4位二进制计数器IC

典型工作电压:5V

工作电压范围:4.5V至5.5V

输出高压:3.5V

输出低电压:0.25V

高时输出电流:-0.4mA

低时输出电流:8mA

CP0和CP1输入时钟频率:分别为32MHz和16MHz。

CP0和CP1脉冲宽度:分别为15nS和30nS。

提供14引脚PDIP,GDIP,PDSO封装

相当于74LS93

74HC19、74LS192、4516

74LS93是使用四个JK触发器构建的递增计数器。CP1和Q0使用一个触发器构成一个mod-2计数器,而带有Q1,Q2和Q3以及三个触发器的CP0构成mod-8计数器。该IC通常通过将mod-2和mod-8组合在一起以形成mod-16递增计数器来使用。该IC通常用于计数应用或2分频,8分频或16分频设计。

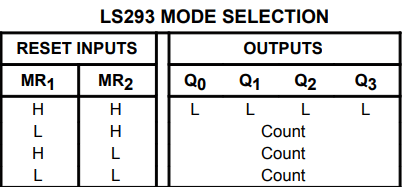

使用74LS93 IC既简单又直接。IC必须由+ 5V的Vcc和接地引脚供电。它有两个MR(主复位)引脚,可用于选择所需的模式。对于正常操作,两个引脚都必须接地,如下表所述。

接下来,对于时钟引脚CP0和CP1,我们必须提供一个时钟脉冲以进行计数。也就是说,对于给这些时钟引脚的每个脉冲,IC会将计数增加1。输出位Q0由CP1控制,输出位Q1,Q2和Q3由CP0控制。为了使用所有四个位,时钟脉冲CP1连接到Q0。

CP0和CP1的最大时钟频率分别可以是32MHz和16MHZ,脉冲宽度应分别最小为15nS和30nS。通常,时钟引脚由555定时器或其他脉冲发生电路驱动。下表中显示输出位递增。

.png)

通过模拟IC可以理解完整的工作。此处,通过将两个MR引脚都接地来选择模式0(计数模式),并且对于时钟脉冲,我正在手动切换逻辑状态以提供脉冲。每当我将引脚设为高电平和低电平时,都会生成一个脉冲。仿真如下所示

用于创建较长的计时周期

不稳定的分频器或计数器电路

定时相关应用

用于应避免使用微控制器的项目

脉冲计数器或分频器

社群二维码

关注“华强商城“微信公众号

Copyright 2010-2023 hqbuy.com,Inc.All right reserved. 服务热线:400-830-6691 粤ICP备05106676号 经营许可证:粤B2-20210308