摘要: 74LS138芯片是TTL逻辑门“ 74xx”系列成员,它可以用于解码或多路分解应用,并具有3输入至8输出设置。74LS138芯片还可用于高性能存储解码或数据路由应用,需要非常短的传播延迟时间。在高性能存储系统中,这些解码器可用于最小化系统解码的影响。74LS138的三个使能引脚(其中两个低电平有效和一个高电平有效)减少了扩展时对外部门或反相器的需求。无需外部反相器即可实现24线解码器,而32线解码器仅需一个反相器。

74LS138芯片是TTL逻辑门“ 74xx”系列成员,它可以用于解码或多路分解应用,并具有3输入至8输出设置。74LS138芯片还可用于高性能存储解码或数据路由应用,需要非常短的传播延迟时间。在高性能存储系统中,这些解码器可用于最小化系统解码的影响。74LS138的三个使能引脚(其中两个低电平有效和一个高电平有效)减少了扩展时对外部门或反相器的需求。无需外部反相器即可实现24线解码器,而32线解码器仅需一个反相器。

74LS138通过将使能引脚用作数据输入引脚而用于多路分解应用。此外,芯片输入还被高性能肖特基二极管钳位,以抑制线路振铃并简化系统设计。

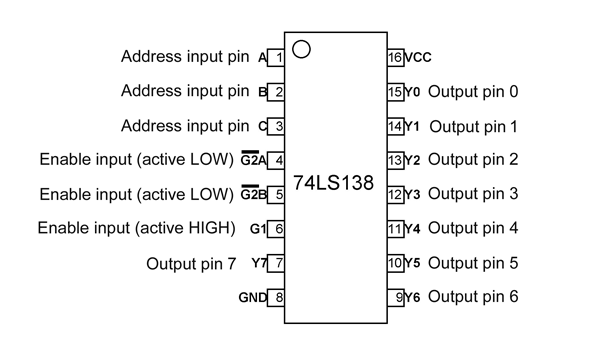

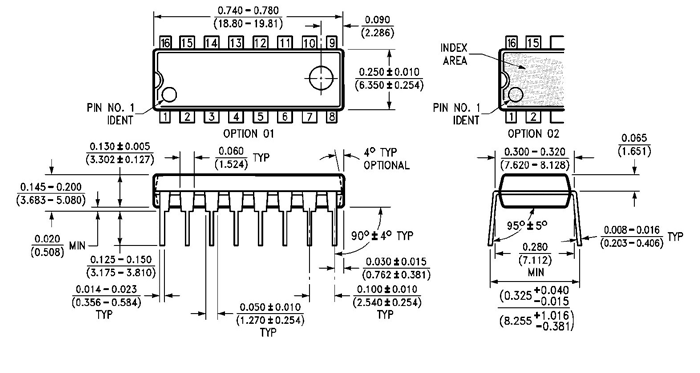

芯片74LS138的引脚图:

芯片74LS138的引脚功能:

| 引脚序号 | 引脚名称 | 引脚功能说明 |

| 1 | A | Address input pin |

| 2 | B | Address input pin |

| 3 | C | Address input pin |

| 4 | G2A | Enable input (active LOW) |

| 5 | G2B | Enable input (active LOW) |

| 6 | G1 | Enable input (active HIGH) |

| 7 | Y7 | Output pin 7 |

| 8 | GND | Ground |

| 9 | Y6 | Output pin 6 |

| 10 | Y5 | Output pin 5 |

| 11 | Y4 | Output pin 4 |

| 12 | Y3 | Output pin 3 |

| 13 | Y2 | Output pin 2 |

| 14 | Y1 | Output pin 1 |

| 15 | Y0 | Output pin 0 |

| 16 | VCC | Power supply pin |

专为高速设计

集成了三个使能引脚以简化级联

解复用能力

肖特基钳位以获得高性能

静电防护

平衡的传播延迟

输入接受高于VCC的电压

电源电压:1.0V至5.5V

典型传播延迟:21nS

低功耗:32mW

工作温度:-40oC至+125oC

74LS138解码器芯片专门设计用于需要非常短的传输延迟时间的高性能存储器解码或数据路由应用。存储器单元的数据交换速率决定了任何应用程序的性能,并且任何类型的延迟在那里都不容忍。在这种应用中,使用74LS138线路解码器是理想选择,因为该设备的延迟时间小于存储器的典型访问时间。这意味着解码器引入的有效系统延迟对影响性能的影响可以忽略不计。

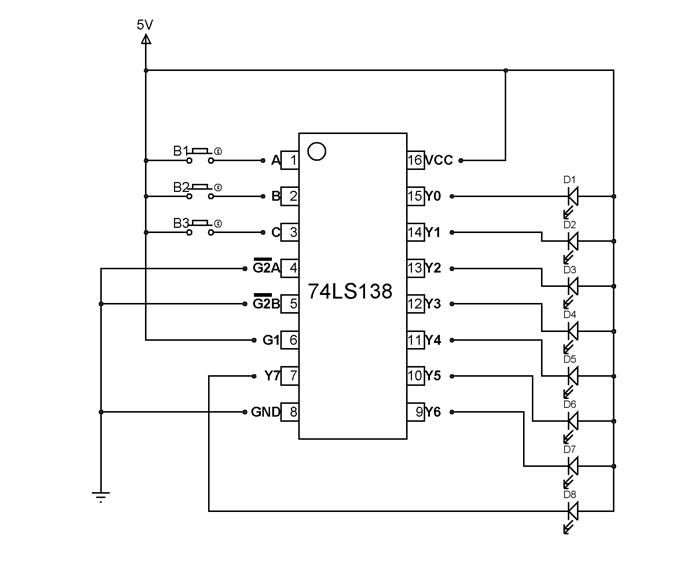

为了理解74LS138芯片的工作原理,让我们构建一个带有一些外部元件的简单应用电路,如下所示。

电路图说明:此处的输出连接到LED,以显示哪个输出引脚变为LOW,并记住器件的输出是反相的。我们使用的是单个设备,因此我们将G2A和G2B引脚接地,然后将G1连接到VCC以启用芯片。这里的三个按钮代表设备的三条输入线。

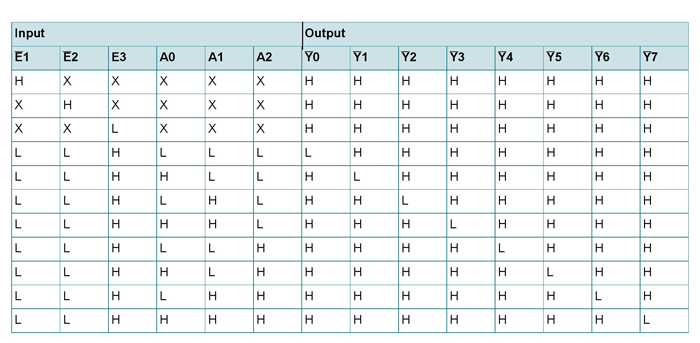

H =高,L =低,X =无关

如表前三行所示,使能引脚需要适当连接,或者与输入线无关,所有输出都将为高。如电路图所示连接使能引脚后,您可以使用输入线获取输出。

上电后,如果未按下所有按钮,则Y0将为低电平,剩余输出将为高电平,如表所示。仅按下B1后,A0 = HIGH,并且Y1将变为LOW,而其余部分将变为HIGH。如果仅按下B2,则A1 = HIGH,并且Y2将变为LOW,而其余部分将变为HIGH。这样,我们可以通过切换三个按钮B1,B2和B3(三个输入A0,A1和A2)来实现所有的真值表,并且我们有三个输入到八个输出解码器。

线路解码器

伺服器

数字系统

线路解复用

电信电路

记忆体电路

社群二维码

关注“华强商城“微信公众号

Copyright 2010-2023 hqbuy.com,Inc.All right reserved. 服务热线:400-830-6691 粤ICP备05106676号 经营许可证:粤B2-20210308