摘要: 全球一号代工厂台积电宣布了有关极紫外光刻(EUV)技术的两项重磅突破。

全球一号代工厂台积电宣布了有关极紫外光刻(EUV)技术的两项重磅突破,一是首次使用7nm EUV工艺完成了客户芯片的流片工作,二是5nm工艺将在2019年4月开始试产。今年4月开始,台积电第一代7nm工艺(CLN7FF/N7)投入量产,苹果A12、华为麒麟980、高通“骁龙855”、AMD下代锐龙/霄龙等处理器都正在或将会使用它制造,但仍在使用传统的深紫外光刻(DUV)技术。

而接下来的第二代7nm工艺(CLNFF+/N7+),台积电将首次应用EUV,不过仅限四个非关键层,以降低风险、加速投产,也借此熟练掌握ASML的新式光刻机Twinscan NXE。

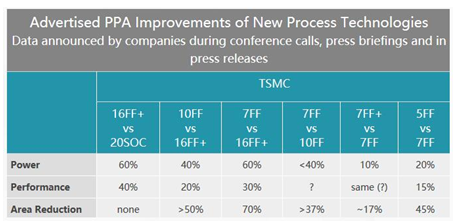

7nm EVU相比于7nm DUV的具体改进公布得还不多,台积电只说能将晶体管密度提升20%,同等频率下功耗可降低6-12%。

如今在7nm EUV工艺上成功完成流片,证明了新工艺新技术的可靠和成熟,为后续量产打下了坚实基础。

台积电没有透露这次流片成功的芯片来自哪家客户,但是想想各家和台积电的合作关系,其实不难猜测。

7nm之后,台积电下一站将是5nm(CLN5FF/N5),将在多达14个层上应用EUV,首次全面普及,号称可比初代7nm工艺晶体管密度提升80%从而将芯片面积缩小45%,还可以同功耗频率提升15%,同频功耗降低20%。

2019年4月,台积电的5nm EUV工艺将开始风险性试产,量产则有望在2020年第二季度开始,正好满足后年底各家旗舰新平台。

台积电5nm工艺的EDA设计工具将在今年11月提供,因此部分客户应该已经开始基于新工艺开发芯片了。

随着半导体工艺的急剧复杂化,不仅开发量产新工艺的成本大幅增加,开发相应芯片也越来越费钱,目前估计平均得花费1.5亿美元,5nm时代可能要2-2.5亿美元。

然而,Intel刚发布的秋季桌面平台仍然都是14nm,而拖延已久的10nm要到明年才能量产,7nm则是遥遥无期,5nm就更别提了。

上一篇:常用的五类光纤传感器基本原理解析

社群二维码

关注“华强商城“微信公众号

Copyright 2010-2023 hqbuy.com,Inc.All right reserved. 服务热线:400-830-6691 粤ICP备05106676号 经营许可证:粤B2-20210308